## Accurate Modeling of the Self-Heating and Trapping Effects in GaN HEMTs

**Yiao Li, Application Engineer Keysight Technologies**

#### **Outline**

- Introduction of GaN HEMTs modeling and new features in ASM-HEMT 101.4 and MVSG\_CMC 3.2.0

- RF parameter extraction package in IC-CAP

- Parameter extraction flow

- Thermal extraction

- Trapping extraction

- Summary

#### RF GaN is Hot

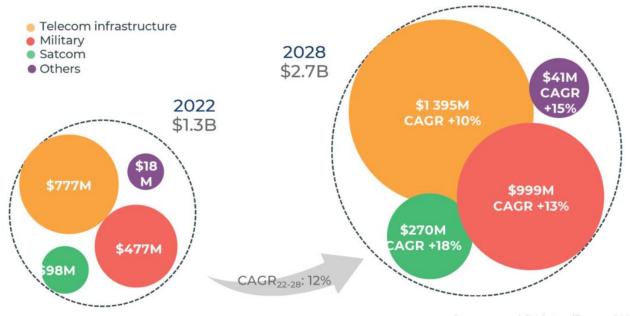

## RF GaN market will grow from \$1.3B to \$2.7B by 2028

#### 2022-2028 RF GAN DEVICE MARKET FORECAST

Source: RF GaN 2023 report, Yole Intelligence, 2023

www.yolegroup.com | ©Yole Intelligence 2023

Source: "RF GaN market broadens its appeal with an appetite for GaN-on-Silicon" - www.yolegroup.com

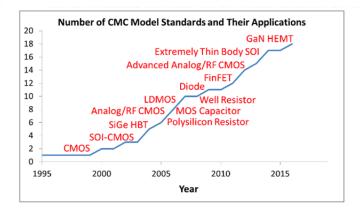

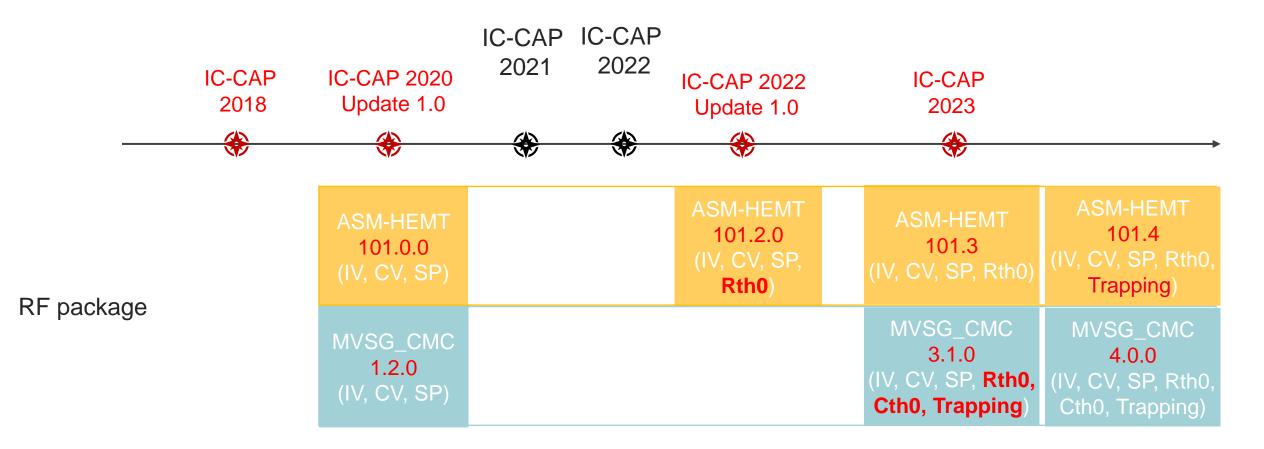

## **GaN Model Development History**

ASM-HEMT 101.4

MVSG\_CMC 3.2.0

Source: "RF GaN market broadens its appeal with an appetite for GaN-on-Silicon" - www.yolegroup.com

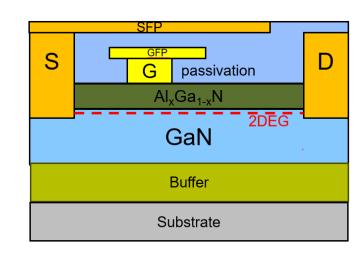

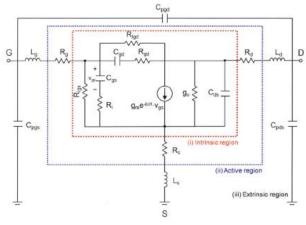

## **Modeling of Various GaN Device Effects**

- <u>Field-plates</u> modeled with computationally efficient formulation

- Non-linear access region physics-based formulation covering linear and saturation

- <u>Gate-current (IG)</u> physics-based formulations covering multiple

IG mechanisms

- <u>Trapping effects</u> multiple modes to suit applications and extraction flows

- Noise Physics-based thermal- and flicker noise models

- <u>Self-heating effect</u> modeled with thermal sub-circuits

- <u>Ambient temperature effects</u> modeled with temperaturedependent formulations

All effects modeled with consistency with each-other

•

Source: Sourabh Khandelwal, "Scalable nonlinear RF modeling of GaN HEMTs with industry standard ASM-HEMT compact model - Enabling new modeling capabilities for GaN" - IMS

#### **ASM-HEMT 101.4 New Features**

- New current saturation formulation added to the access region resistance model

- Two new model parameters tepi and asub added to tune the substrate voltage dependence of pinch-off voltage

- Technical manual updated with new section 5.2 describing statical model extraction flow

Source: Release notes of ASM-HEMT 101.4

## **MVSG\_CMC 3.2.0 New Features**

- External thermal node added additional temperature offset can be defined at the netlist level

- Schottky p-GaN implementation to include dynamic Vt effect

Source: release notes of MVSG\_CMC 3.2.0

#### **Outline**

- Introduction of GaN HEMTs modeling and new features in ASM-HEMT 101.4 and MVSG\_CMC 3.2.0

- RF parameter extraction package in IC-CAP

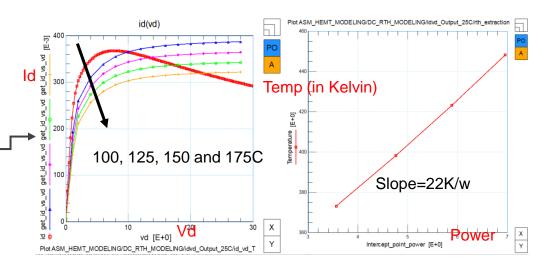

- Parameter extraction flow

- Thermal extraction

- Trapping extraction

- Summary

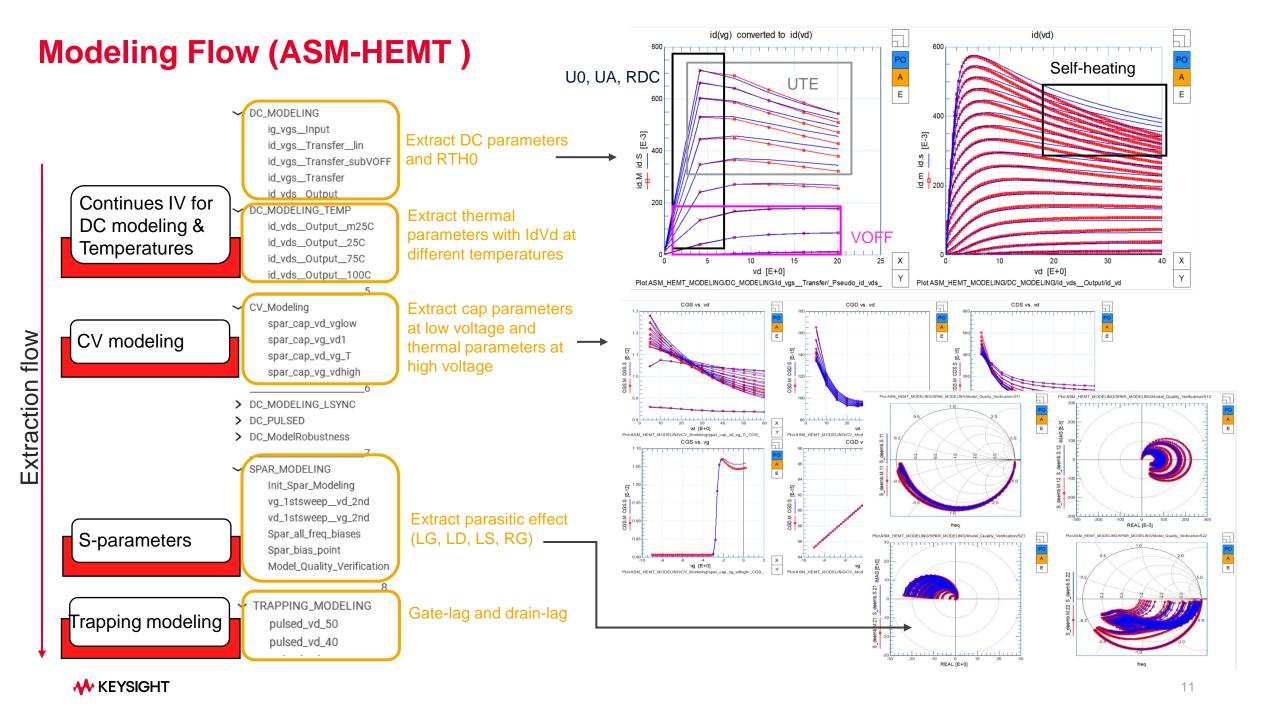

## ASM and MVSG Modeling Packages Updates in IC-CAP

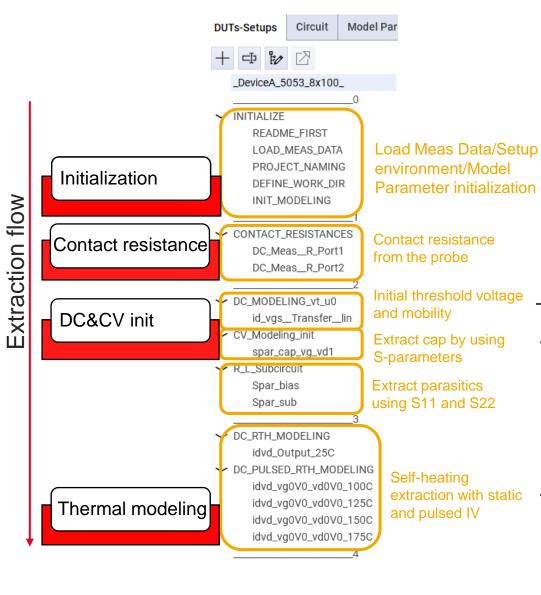

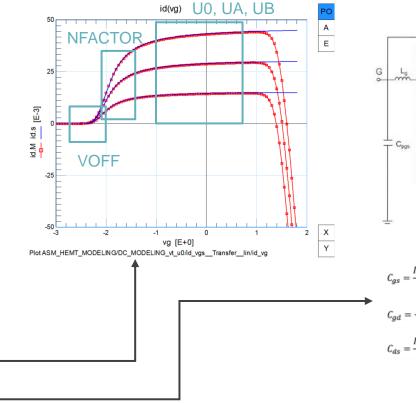

## **Modeling Flow (ASM-HEMT)**

## **MVSG\_CMC** Parameter Extraction in IC-CAP

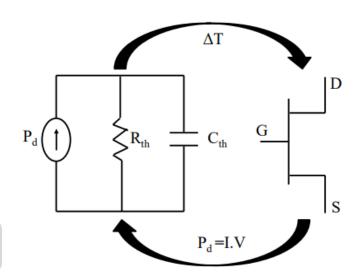

## **Self-Heating Effect**

- Self-heating effect has become a greater concern for industry in recent years. Since smaller devices, new materials and geometries, resulting in an increase of this effect.

- Self-heating results in an increase of the device temperature will cause mobility reduction, compromised reliability and signal delays.

- In ASM-HEMT and MVSG\_CMC models, self-heating effect is modeled by standard R-C network, which contains thermal resistance RTH0 and thermal capacitance CTH0.

Source: S. Khandelwal et al., " ASM-HEMT 101.2.0 Advanced SPICE Model for HEMTs," Technical Manual [2020].

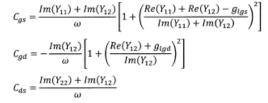

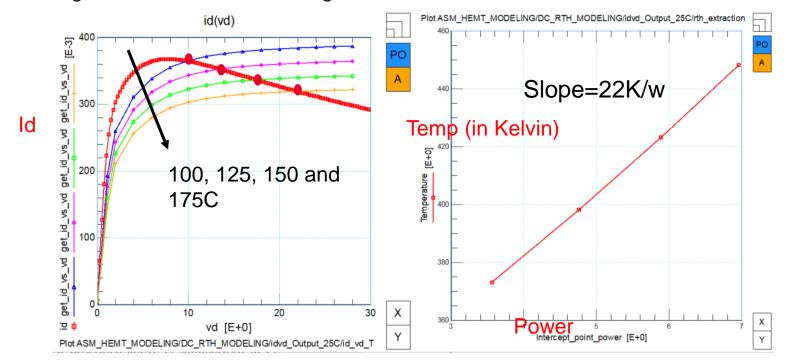

## **Self-heating Extraction**

- We need two types of data:

- Static IdVd at room temperature.

- Pulsed IdVd at various other than the room temperature.

- Vd0=0V and Vg0=0V, which are the voltage at low level.

DC, T1=25C Pulsed from (0,0), T2=100C DC curve:  $T1 = T1_{ambient} + RTH0 \cdot P_{diss1}$ Pulsed curve:  $T2 = T2_{ambient} + RTH0 \cdot P_{diss2}$  $RTH0 = (T1_{ambient} - T2_{ambient})/P_{diss1}$

## **Trapping Effect**

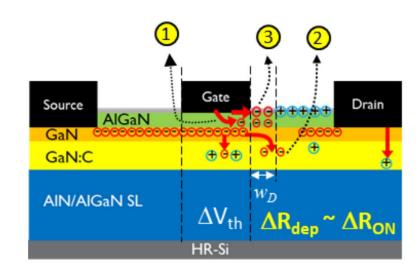

#### **Introduction of Trapping Effect**

Charge trapping in the buffer layer and AlGaN/GaN interface layer cause a reduction in 2DEG channel charge density, causing a modulation of drain current  $I_D$ .

The trap model accurately captures Dynamic-R<sub>ON</sub> and knee walkout.

#### **Gate-lag**

- Vdq = 0V

- Vgq = Deep OFF condition:

A strong field through the

AlGaN layer. No field through buffer (since Vds = 0). Only surface traps activated.

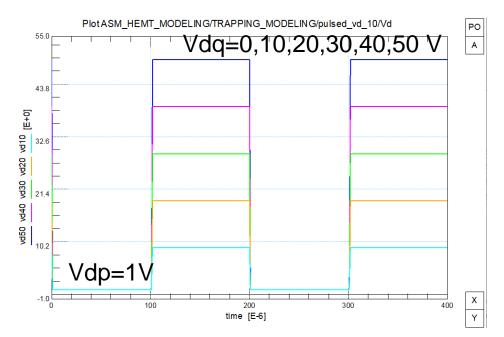

#### **Drain-lag**

- Vdq = A significantly positive voltage

- Vgq = Deep OFF condition:

A strong field through the AlGaN layer as well as the buffer. Both surface and buffer traps activated.

Source: R. Fang, D. Ma, U. Radhakrishna, and L. Wei, "MVSG GaN-HEMT Model: Approach to Simulate Fringing Field Capacitances, Gate Current De-biasing, and Charge Trapping Effects," accepted by 2022 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium

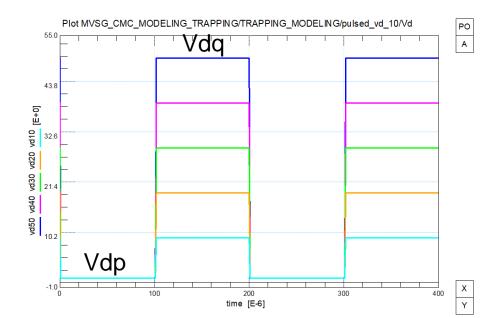

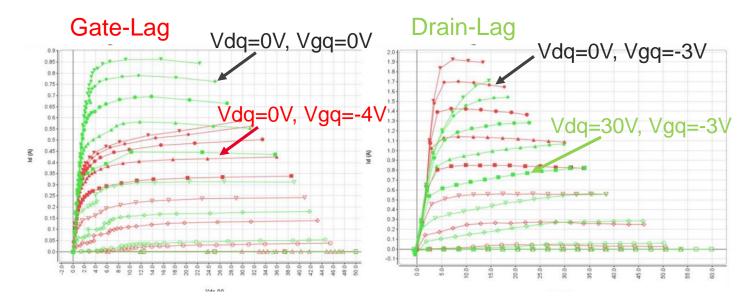

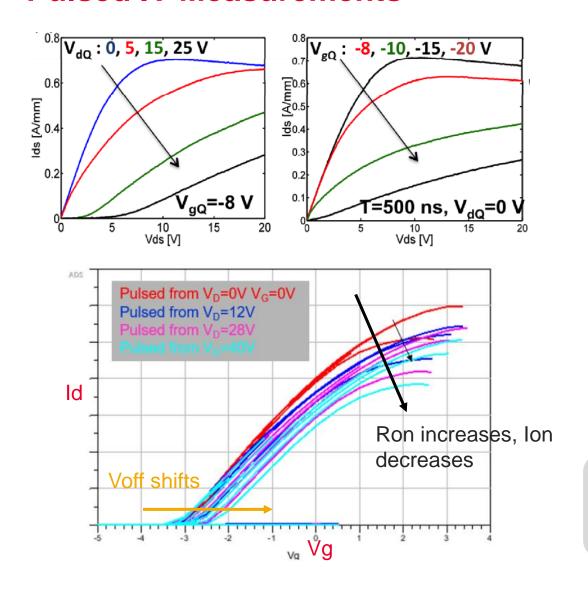

#### **Pulsed IV Measurements**

- Decrease of Ion, increase of Ron and Vdsat

- After voltage stress is removed, a non-negligible time is required for the 2DEG to regain charge.

- Critical for circuit dynamic operations for RF.

Increase of Ron and cut-off voltage

Source: U. Radhakrishna, D. Piedra, Y. Zhang, T. Palacios and D. Antoniadis, "High voltage GaN HEMT compact model: Experimental verification, field plate optimization and charge trapping," 2013 IEEE International Electron Devices Meeting, Washington,

U. Radhakrishna and L. Wei, "MIT virtual source GaN HEMT: MVSG model manual," May 1 2022

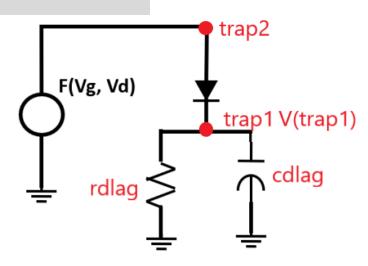

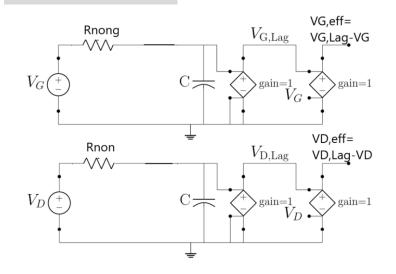

**ASM-HEMT Trapping Model 1 and 2**

- TRAPMOD=0

Trapping model turns off

- TRAPMOD=1

- A single RC sub-circuit

- Trap voltage V(trap1) will feed back into model

- voff\_cap, eta0\_cap, rs\_cap, rd\_cap changing due to the trapping

- TRAPMOD=2

- Two RC sub-circuits are used

- Vtrap1 and Vtrap2 will feed back into model

- Voff\_trap, ron\_trap, cdscd\_trap, eta0\_trap changing due to the trapping

#### TRAPMOD=1

#### TRAPMOD=2

Source: S. Khandelwal, J. Hodges, and N. Reddy, ASM-HEMT 101.3.0 Advanced SPICE Model for HEMTs Technical Manual, Macquarie University

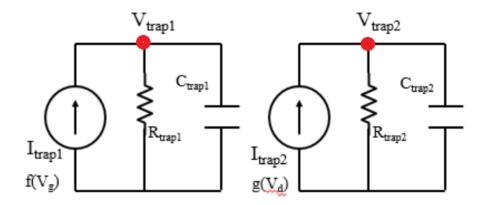

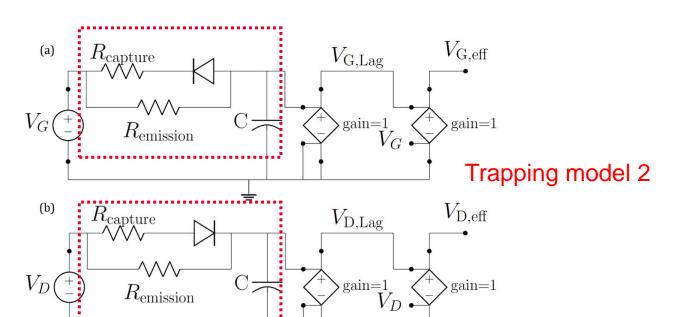

#### **ASM-HEMT Trapping Model 3 and 4**

- TRAPMOD=3

- Single RC sub-circuit

- Recommended for GaN power device dynamic ON-resistance

- Only drain-side resistance is affected

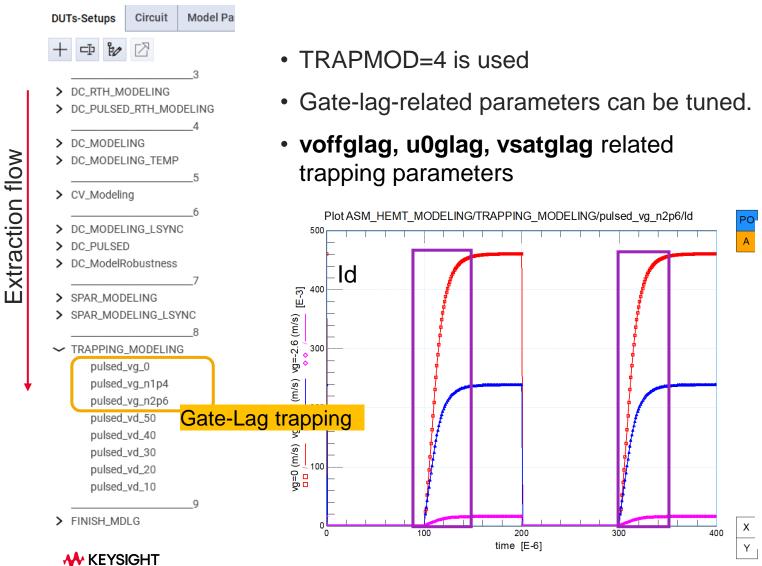

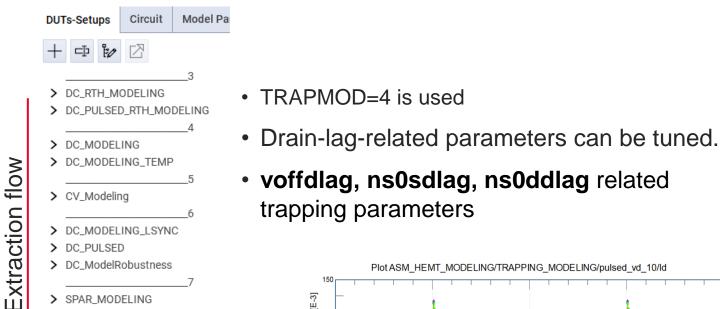

- TRAPMOD=4

- Two RC sub-circuits are used

- Model drain-lag and gate-lag with most flexibility

- voffglag, u0glag, vsatglag changing due to gate-lag  $(V_{G,eff})$

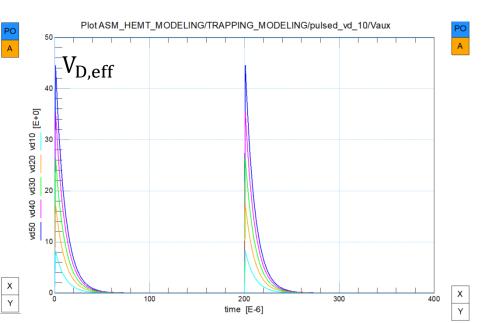

- voffdlag, ns0sdlag, ns0ddlag changing due to drain-lag  $(V_{D,eff})$

#### TRAPMOD=3

#### TRAPMOD=4

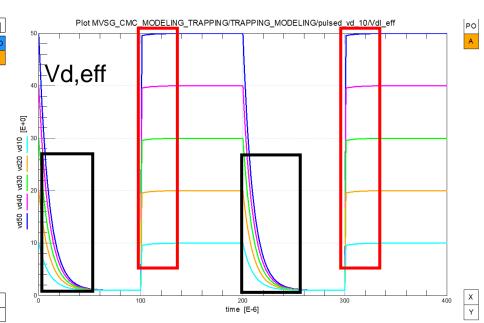

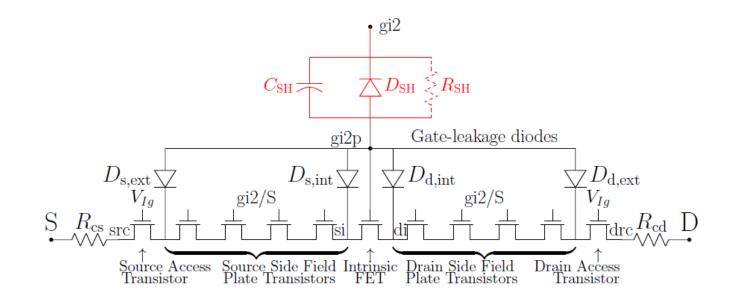

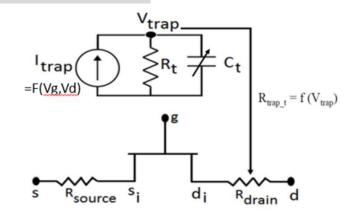

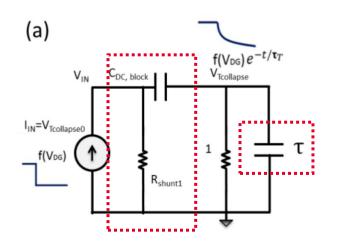

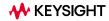

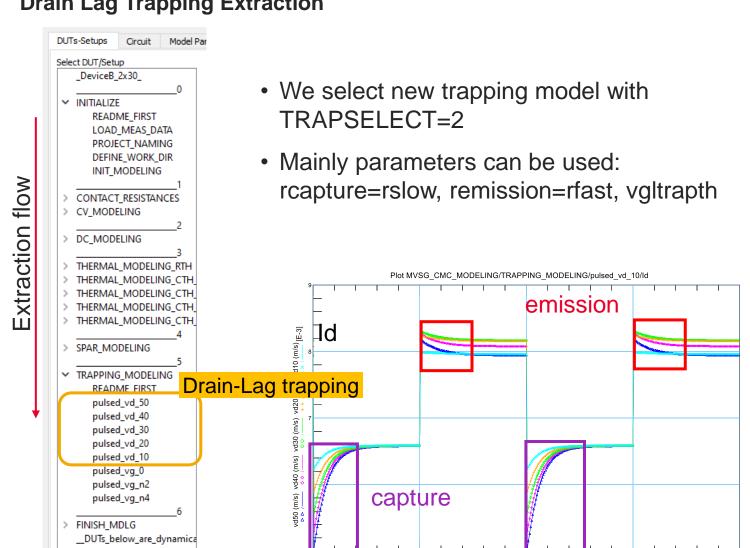

**MVSG\_CMC Charge Trapping Model**

TRAPSELECT=0

Trapping model turns off

TRAPSELECT=1

A single RC network with a constant time  $\tau$  is used for modeling trapping and de-trapping constant time.

#### TRAPSELECT=2 (new)

Two parallel R-branches in an RC network with an ideal series diode on one of the resistance branches.

Two-time constants are used.

Recommended due to more flexibility

Trapping model 1

Source: R. Fang, D. Ma, U. Radhakrishna, and L. Wei, "MVSG GaN-HEMT Model: Approach to Simulate Fringing Field Capacitances, Gate Current De-biasing, and Charge Trapping Effects," accepted by 2022 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium

$au_{capture}^{\perp} \approx R_{capture}C$  in forward-biased  $au_{emission} \approx R_{emission}C$  in reverse-biased

## **Trapping Extraction (ASM-HEMT)**

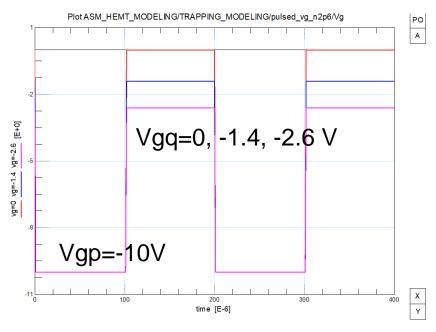

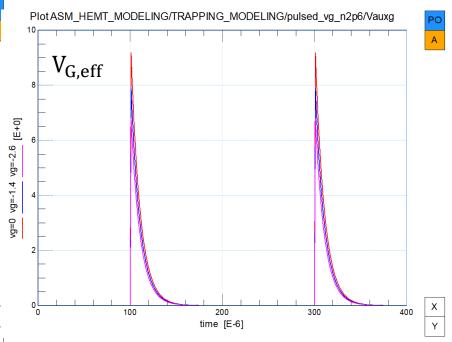

#### **Gate Lag Trapping Extraction**

## **Trapping Extraction (ASM-HEMT)**

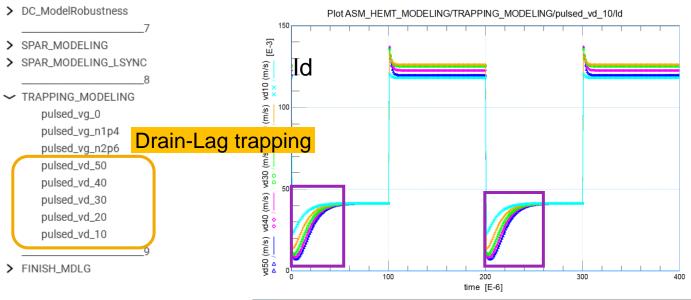

#### **Drain Lag Trapping Extraction**

## **Summary**

- The latest version of ASM-HEMT 101.4 and MVSG\_CMC 3.2.0 is implemented in ADS 2024 update 1

- The RF package with ASM-HEMT 101.3 and MVSG\_CMC 3.1.0 is implemented in IC-CAP 2023 and newer version

- Both ASM-HEMT and MVSG\_CMC have good performance on GaN HEMTs modeling:

- Core model for DC

- CV and S-parameters

- Thermal extraction implemented in both ASM-HEMT and MVSG\_CMC parameter flow

- Trapping extraction implemented in MVSG\_CMC parameter flow will implement in ASM-HEMT parameter flow soon

#### **Thanks**

- Thanks to Prof. Sourabh Khandelwal, developer of ASM-HEMT, for his help in the development of ASM-HEMT parameter flow in IC-CAP

- Thanks to Prof. Lan Wei, developer of MVSG\_CMC, for her help in the development of MVSG\_CMC parameter flow in IC-CAP

# Thank you

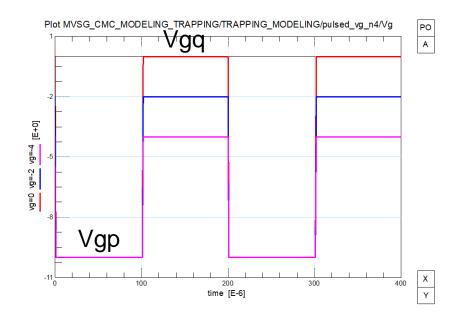

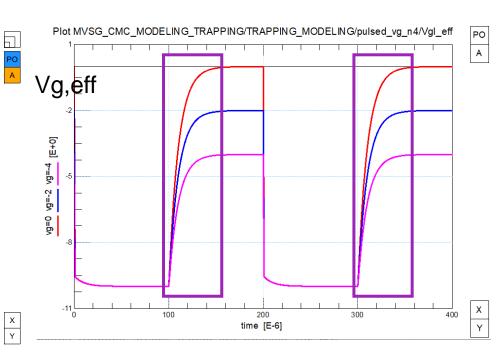

#### **Gate Lag Trapping Extraction**

time [E-6]

\_\_DUTs\_below\_are\_dynamica

FINISH MDLG

#### **Drain Lag Trapping Extraction**

time [E-6]